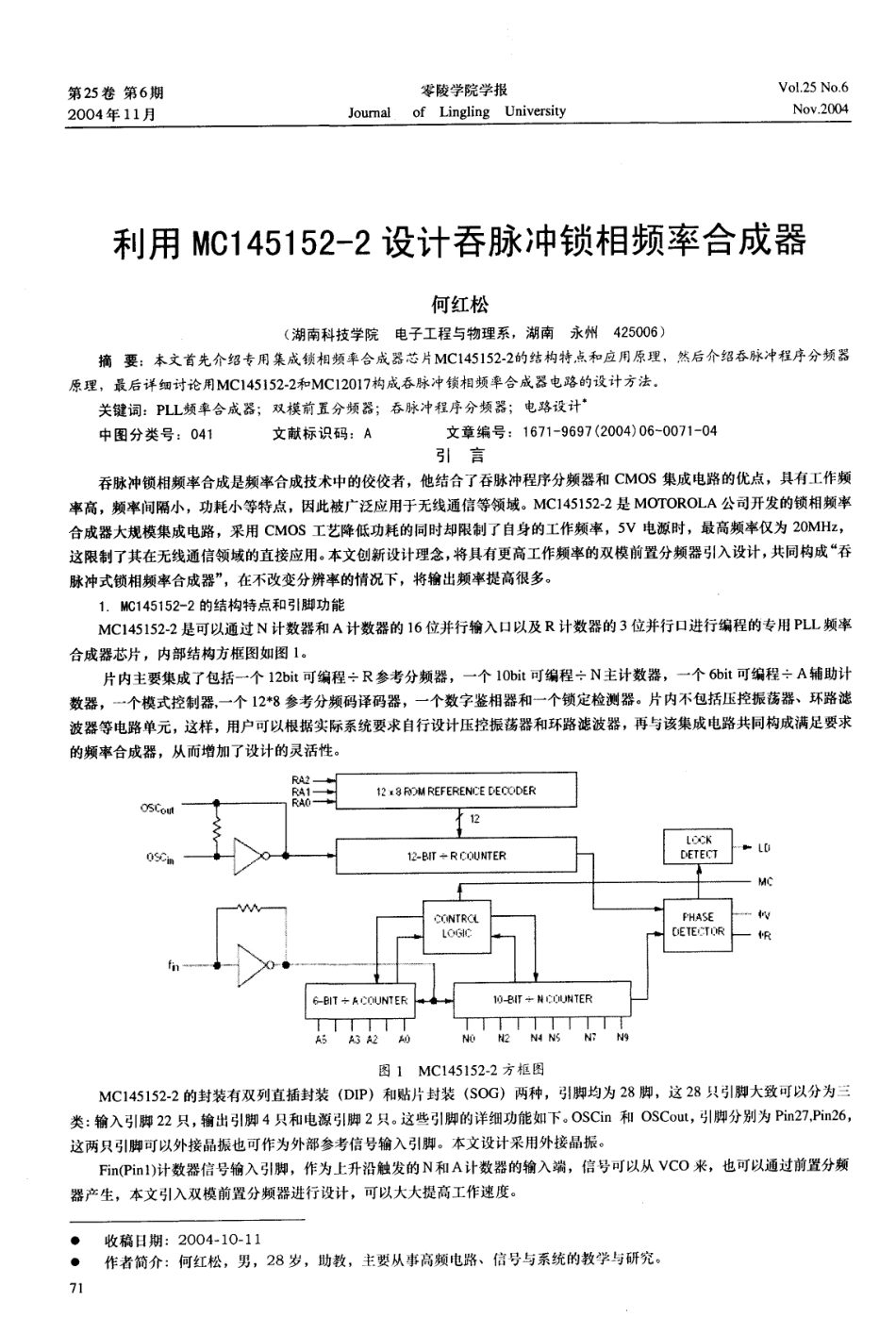

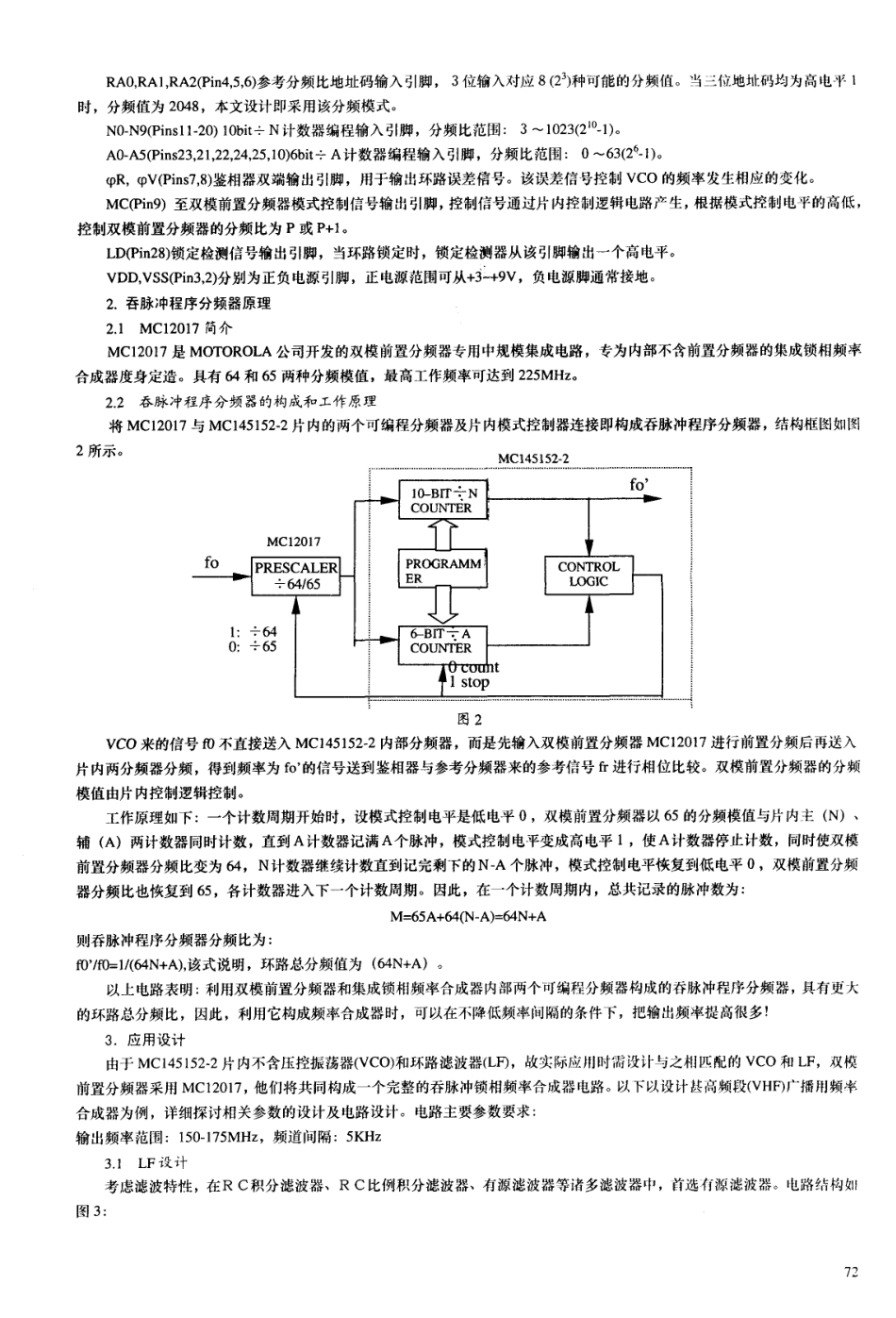

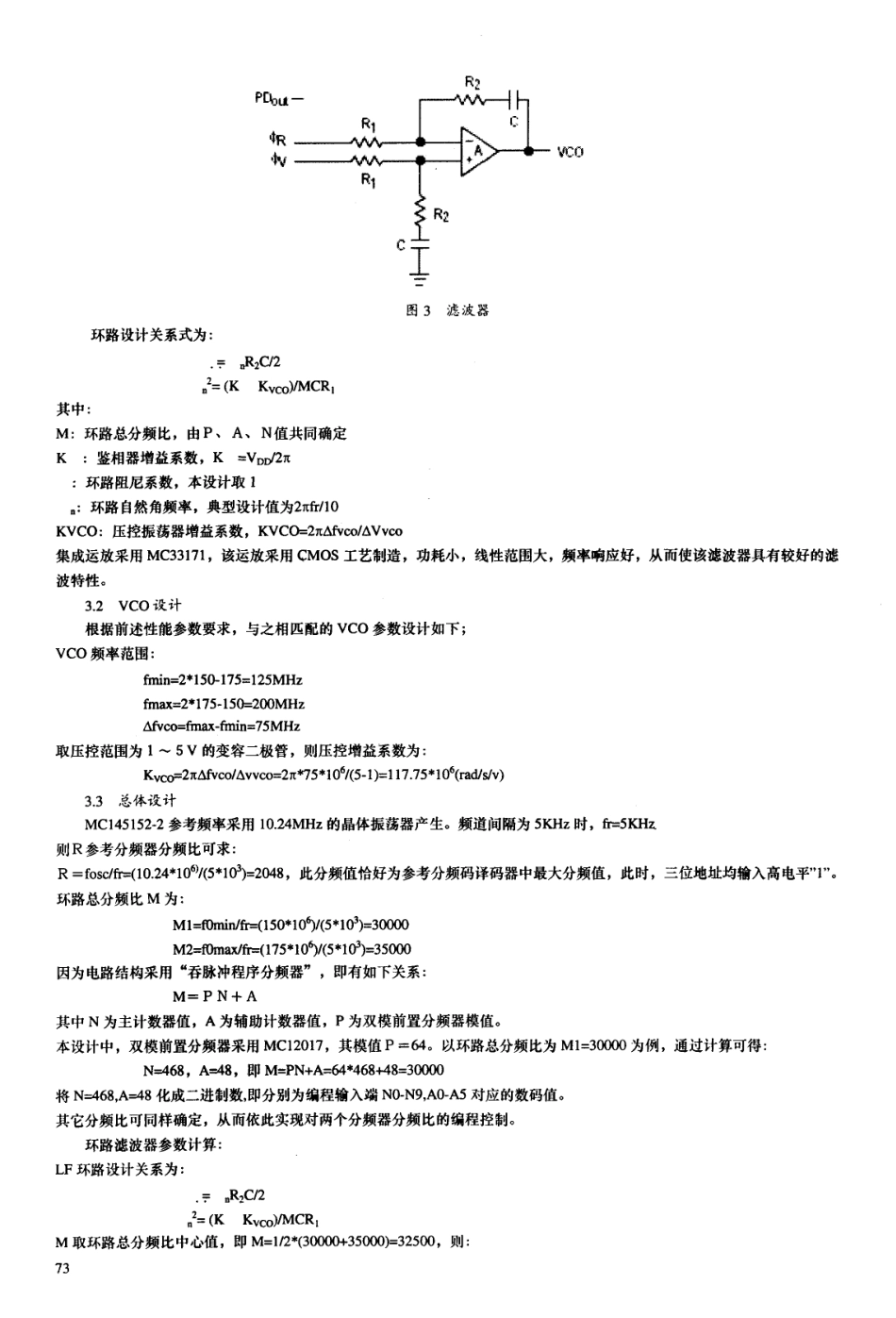

零陵学院学报第25卷 第6期2004 年 11月Journal of Lingling UniversityVo1.25 No.6 Nov.2004利用MC145152-2设计吞脉冲锁相频率合成器 何红松 (湖南科技学院电子工程与物理系,湖南 永州 425006) 摘 要: 本文首先介绍专用集成锁相频率合成器芯片MC145152-2的结构特点和应用原理,然后介绍吞脉冲程序分频器原理,最后详细讨论用MC 145152-2和MC 12017构成吞脉冲锁相频率合成器电路的设计方法。 关键词: PLL频率合成器; 双模前置分频器; 吞脉冲程序分频器; 电路设计* 中图分类号: 041文献标识码: A文章编号: 1671- 9697(2004)06- 0071- 04 引言 吞脉冲锁相频率合成是频率合成技术中的佼佼者,他结合了吞脉冲程序分频器和 CMOS 集成电路的优点,具有工作频率高,频率间隔小,功耗小等特点,因此被广泛应用于无线通信等领域。MC 145152-2是MOTOROLA公司开发的锁相频率合成器大规模集成电路,采用 CMOS 工艺降低功耗的同时却限制了自身的工作频率,5V 电源时,最高频率仅为 20MHz,这限制了其在无线通信领域的直接应用。本文创新设计理念,将具有更高工作频率的双模前置分频器引入设计,共同构成“吞脉冲式锁相频率合成器”,在不改变分辨率的情况下,将输出频率提高很多。 1. MC145152- 2 的结构特点和引脚功能 MC 145152-2 是可以通过N计数器和A计数器的16位并行输入口以及R计数器的3位并行口进行编程的专用PLL频率合成器芯片,内部结构方框图如图 to 片内主要集成了包括一个 12bit 可编程= R参考分频器,一个 l Obit可编程= N主计数器,一个6bit 可编程= A辅助计数器,一个模式控制器,一个 12*8 参考分频码译码器,一个数字鉴相器和一个锁定检测器。片内不包括压控振荡器、环路滤波器等电路单元,这样,用户可以根据实际系统要求自行设计压控振荡器和环路滤波器,再与该集成电路共同构成满足要求的频率合成器,从而增加了设计的灵活性。05}-in 图 1 MC145152-2 万4C.图 MC 145152-2 的封装有双列直插封装 (DIP) 和贴片封装 (SOG) 两种,引脚均为28 脚,这28 只引脚大致可以分为三类: 输入引脚22 只,输出引脚4 只和电源引脚2只。这些引脚的详细功能如下。OSCin 和 OSCout,引脚分别为Pin27,Pin26,这两只引脚可以外接晶振也可作为外部参考信号输入引脚。本文设计采用外接晶振。 Fin(Pinl)计数器信号输入引脚,作为上升沿触发的N和A计数器的输入端,信号可以从VCO来,也可以通过前置分频器产生,本文引入双模前置分频器进行设计,可以大大提高工作速度。收稿日期: 2004- 10- 11作者简介: 何红松,男,28 岁,助教,主要从事高频电路、信号与系统的教学与研究。:71 RAO,RA 1,RA2(Pin4,5,6)参考分频比地址码输入引脚,3位输入对应8(2 3)种可能的分频值。当三位地址码均为高电平1时,分频值为2048,本文设计即采用该分频模式。 NO-N9(Pins11-20) 1Obit = N计数器编程输入引脚,分频比范围: 3一1023(2 0-1)a AO-A5(Pins23,21,22,24,25,10)6bit= A计数器编程输入引脚,分频比范围: 0一 63(26-1)a cpR, cpV(Pins7,8)鉴相器双端输出引脚,用于输出环路误差信号。该误差信号控制VCO的频率发生相应的变化。 MC(Pin9) 至双模前置分频器模式控制信号输出引脚,控制信号通过片内控制逻辑电路产生,根据模式控制电平的高低,控制双模前置分频器的分频比为P或P+lo LD(Pin28)锁定检测信号翰出引脚,当环路锁定时,锁定检测器从该引脚输出一个高电平。 VDD,VSS(Pin3,2)分别为正负电源引脚,正电源范围可从+3-+9V,负电源脚通常接地。 2. 吞脉冲程序分频器原理 2.1 MC12017 简介 MC12017是MOTOROLA公司开发的双模前置分频器专用中规模集成电路,专为内部不含前置分频器的集成锁相频率合成器度身定造。具有64和65两种分频模值,最高工作频率可达到225MHzo 2.2吞脉冲程序分频器的构成和工作原理 将MC 12017与MC 145152-2片内的两个可编程分频器及片内模式控制器连接即构成吞脉冲程序分频器,结构框图如图2 所示。MC145152-2 图 2 VCO来的信号f0 不直接送入MC145152-2 内部分频器,而...